SmartNIC ~DPDK入門 第15回~

ネットワークパケット処理におけるヘテロジニアスコンピューティングに関連してSmartNICについてご紹介します

DPDK入門

- 2022年12月22日公開

はじめに

こんにちは、NTTテクノクロスの山下です。第13回、第14回で触れましたが、ネットワークパケット処理の世界でも、CPU以外のプロセッサも併用するヘテロジニアスコンピューティングが登場してきています。今回は高機能なNICであるSmartNICについて紹介したいと思います。

SmartNICが必要とされる背景

SmartNICのご紹介の前に、SmartNICが必要となる背景について考えてみました。

私個人が受けている印象ではありますが、ネットワークに流れるデータ量は、多くなっていると思います。

また、同時に、あるパケットを取り出したときにパケットサイズが大きかったり、その構造が複雑になっている場合があると思います。

これには様々な要因があるとおもいますが、例えば以下の2つの要因が関連すると考えます。

A)ネットワークパケットの暗号化

B)仮想化によるトンネリング(カプセル化)

まず、Aについて解説します。暗号化されないパケットはNW機器あるいはネットワークケーブルにタップ(接続)することによりその内容を読み取ることができます。

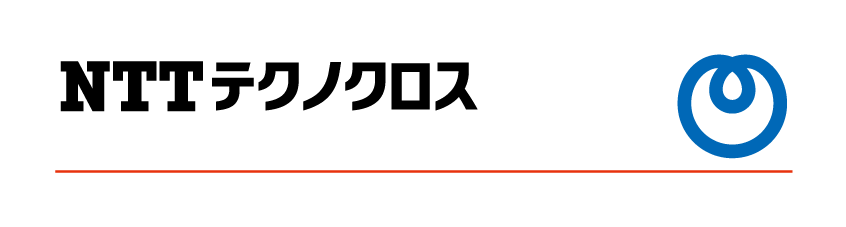

クレジットカードや生年月日・住所をはじめ、企業間の通信、あるいは個人間の通信であっても他人に知られたくない情報は多いと思います。そのような情報はパケット単位や、通信経路全体が暗号化されます(IPSec,TLS,MACSecurityなど用途により利用するプロトコルは変わります)。このような暗号化を行うと一般的に、暗号化前にくらべて暗号化後の方がパケット全体のサイズが大きくなります。図1はIPsecプロトコルでVPNゲートウェイ間を暗号化した場合に、どのようにパケットサイズが増えるかを簡単に示しています。

図1.IPsecVPNでパケットサイズが増える例

次にBについて解説します。

仮想化技術の進歩により、多くのインターネット上のサービスはデータセンタ内の仮想マシン(Virtual Machine(VM))上で実行されています。

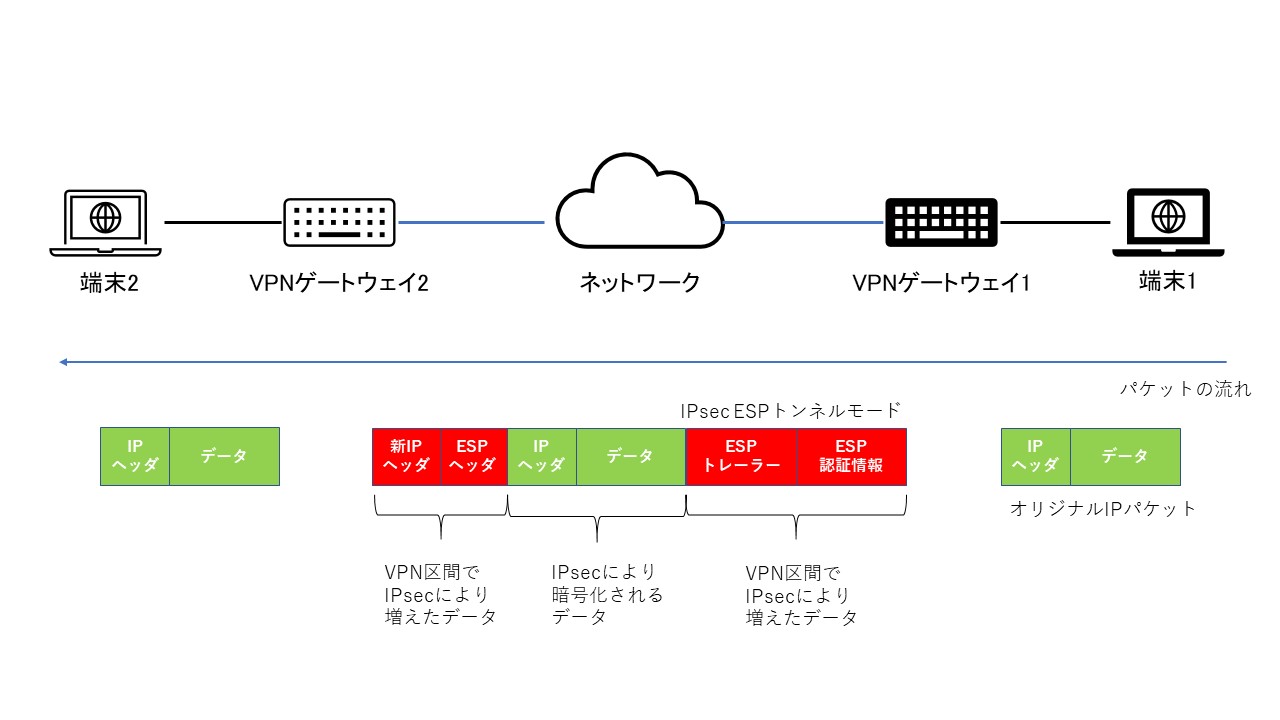

このときデータセンタ内では、あるパケットがどの仮想マシンあてのパケットであるかを識別ためにVXLAN, GENEVE, NVGREなどを利用したトンネリング(カプセル化)技術が利用されています。

このカプセル化も、カプセル化前よりカプセル化後の方がパケット全体のサイズが大きくなります。図2はVXLANでトンネリングした場合を示しています。Aと異なり、オリジナルのペイロードは暗号化されませんがパケット全体のサイズが大きくなることが分かると思います。

図2.VXLANでパケットサイズが増える例

第14回でも、紹介しましたが、今日におけるCPU処理のボトルネックの要因の一つとして、CPUとメモリ間のメモリバスに大量にデータが流れることが可能性として存在します。

上記のA,Bについては1つのパケットのサイズが大きくなる要因になるため、CPU単独で処理を行った場合、CPUのボトルネックに遭遇する(そしてその結果として処理が遅くなる)可能性が高まります。

SmartNICとは

さて、本題です。SmartNICとは、なんでしょうか?

実は、国際標準などで決められた定義はありません。

以下では、私なりに考えるSmartNICとは、何かについて述べます。文字通り解釈すれば、「Smart(かしこい)」なNIC(Network Interface Card)です。

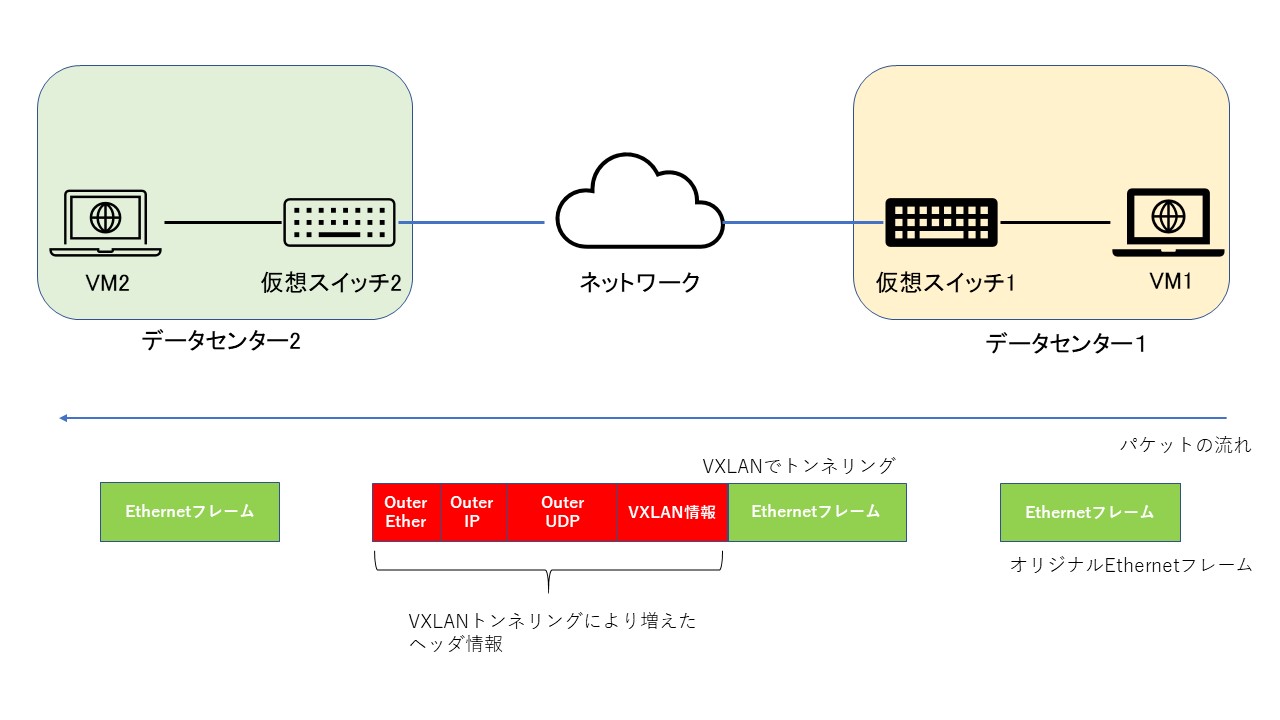

では、「SmartではないNIC」(以降は「通常NIC」と呼ぶ)とはなんでしょうか?OSIモデルで規定される下から2層目のデータリンク層までを扱うのが一般的な「SmartではないNIC」であると考えます。データリンク層では、MACアドレスをアドレスとして持ちますが、これはOSが付与するものではなくNICごとにユニークなものが出荷時に付与されています。また、データリンク層の衝突回避方式として有名なCSMA/CDなどはOSのプロトコルスタックではなく、NIC自身が制御しています。逆を言うと、ネットワーク層(IPレイヤ)以上は、OSのプロトコルスタックで制御しなければなりません。

SmartNICは、この概念を拡張して、ネットワーク層以上のプロトコル処理の一部(あるいは全部)を実行できるものの総称であると私は考えています。図3にイメージを示します。

図3.通常NICとSmartNICの違い

NICで多くの処理をしてくれるならば、ホスト側で実行しなければならないことは相対的に少なくなるため、ホスト側のCPU時間はビジネスロジックにより多く使用することができます。

具体的には、図1で示したIPsec暗号化・復号化処理をSmartNICに任せてしまえば、ホスト側は暗号化・復号化処理にとらわれる必要性がなくなります。

SmartNICの種類

SmartNICはどのような回路で構成されるかにより、大別すると以下の3種類の実装があります。

- a)ASIC-SmartNIC

- b)FPGA-SmartNIC

- c)SoC-SmartNIC

a)ASIC-SmartNIC

ASIC-SmartNICですが通常NICと同様にASIC(application specific integrated circuit、特定用途向け集積回路)で作られています。

ASICの特徴としては、最適化された回路なので処理速度が非常に速いです。ただし、ドライバなどを通じて設定情報を書き換えることは可能ですが、ホスト側からC言語などでのプログラムは原則不可能です。

b)FPGA-SmartNIC

FPGA(field-programmable gate array)は、製造後に購入者や設計者が構成を設定できる集積回路であり、広義にはPLD(プログラマブルロジックデバイス)の一種です。

FPGA-SmartNICは上記の定義通り、プログラム可能なので動作を大きく変えられます。構成によってはユーザごとに異なる場合が多いビジネスロジックもFPGAで構成可能となります。

処理速度に関してはASICほどでないにせよ、一般的なCPU上でのプログラムよりも高速に処理が可能です。

一つ大きな課題があるとするとFPGA上でのプログラムを作るには、HDL(Hardware Definition Language)などハードウェア言語を利用する必要があるため、C/C++などの高級言語を利用するソフトウェア開発者には開発の敷居が高い、ということです(ただし、高位合成ツールなど高級言語で記述可能な手段もあります)

c)SoC-SmartNIC

System-on-a-chip(SOC、SoC)は集積回路の1個のチップ上に、プロセッサコアをはじめ一般的なマイクロコントローラが持つような機能の他、応用目的の機能なども集積し、連携してシステムとして機能するよう設計されている、集積回路製品のことをいいます。(wikipediaより)

大まかにいうと、SoCには通常ホスト側にしかないCPU相当がNIC内に組み込まれているのでプログラムの変更も可能でなおかつ、FPGAのようにHDLなどを使わなくてもプログラミングが可能な分、

ソフトウェア開発者にとっては敷居が低いです。

まとめ

ここまで書くと「SoC-SmartNIC」が一番賢そうだから、それを使えばよいのでは?というように思われるかもしれません。

ただし、一般に価格はASIC-SmartNIC < FPGA-SmartNIC < SoC-SmartNIC と高額になる傾向があります。

また、フルにその能力を活かしきるためには、FPGAなりSoCなりの上にビジネスロジックを構築する必要があり、ユーザ側の開発の負担も大きくなるのです。

上記から、そもそもSmartNICを利用するかしないか、利用するとしてもどのタイプのSmartNICを利用するかは、ユーザ次第、となります。

(具体的には、たとえば既存処理でIPsec処理がCPU処理時間を圧迫している最大要因だとわかれば、ASIC-SmartNICを利用すれば解決できる可能性が高いので、わざわざFPGA-SmartNICやSoC-SmartNICを利用する必然性がない等)

おわりに

今回はヘテロジニアスコンピューティングに関連してSmartNICについてご紹介しました。次回はDPDKにおいてSmartNICを制御する技術の一つであるrte_flowについて解説します。本記事の連載に関して何か問い合わせがございましたら、以下に連絡下さい。よろしくお願いします。

本件に関するお問い合わせ

[著者プロフィール]

フューチャーネットワーク事業部 第一ビジネスユニット

山下 英之(YAMASHITA HIDEYUKI)